Introduction

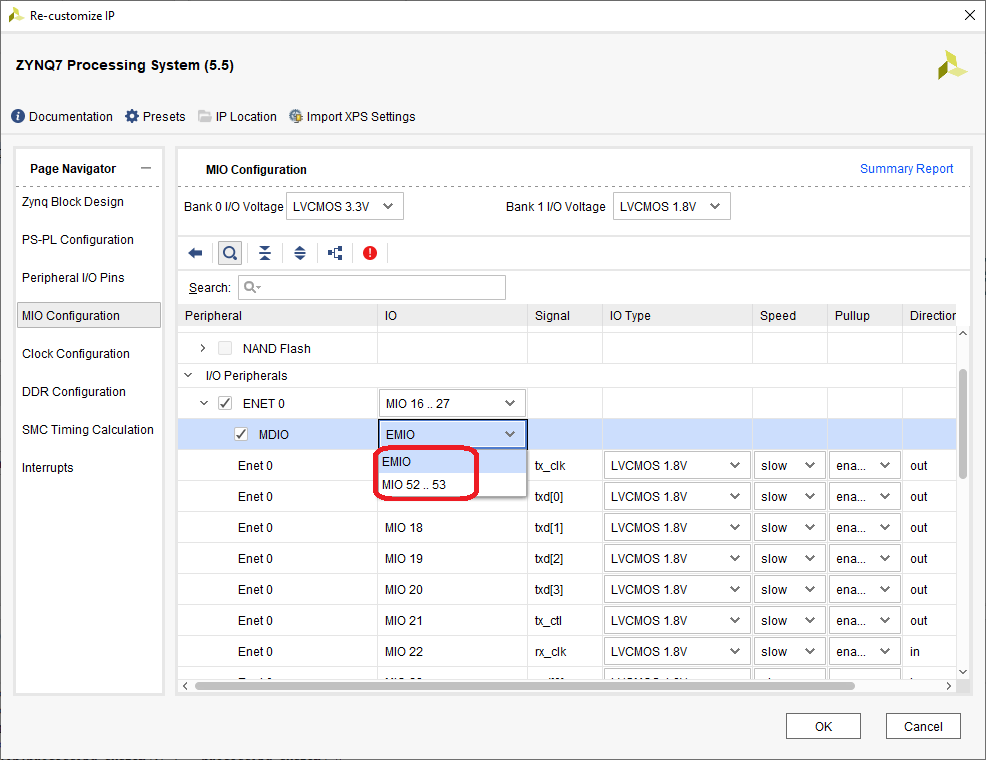

Have you ever experienced limitations of the Zynq/Ultrascale MPSoCs from Xilinx when it comes to GEMs and MDIO interfaces? The thing is that only specific GPIO pins can be used for MDIO communication. As seen on the picture below, apart from EMIO (PL pins) only MIO 52 and 53 can be used to drive a PHY chip on ENET 0. Besides, those MIO 52 and 53 can’t be used for ENET 1.

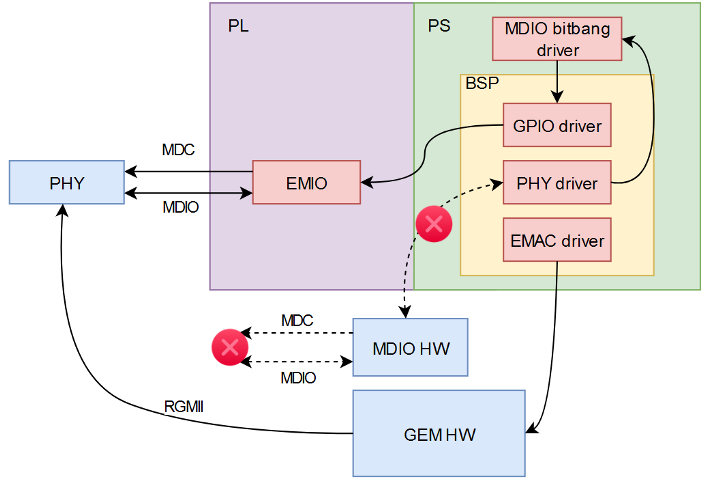

So what happens if you have fully exhausted EMIO pins in your design? Or due to some circumstance MIO 52 and 53 can’t be used? Or by mistake some other MIO pins have been routed to the PHY chip, is there any way to make it work? Actually, there is. In fact, there is a solution to drive MDIO interface by means of any GPIO pin, be it MIO or EMIO. The idea is to drive any two GPIO pins the same way the MDIO hardware block does. And then simply remap the EMAC driver to use our own functions for reading and writing PHY registers while disabling the MDIO hardware block. Now there is an alternative way of driving a PHY as it is shown on the picture below.

Why it is so important to communicate to PHY you may ask. It doesn’t have to be actively driven if it is impossible or difficult to do so, instead, a PHY chip could be configured by boot strap resistors. That is true but there are some caveats:

- Boot strap resistors configure PHY chips to work in one fixed mode, be it 10Mbps, 100Mbps, 1Gbps or auto negotiation mode. Once a mode is chosen it can’t be changed without hardware modifications;

- Boot strap resistors don’t solve the problem of communication with a PHY which means that in this case hardware won’t generate LINK UP / LINK DOWN events and our software stack will be totally unaware of a presence or absence of a physical link;

Suggested solution

We are presenting a fully functional proof of concept application which demonstrates a feasibility of driving MDIO/MDC lines via any GPIO pins for Zynq/Ultrascale powered systems. Our project targets ARTY Z7 boards with Zynq7000 MPSoCs and Vivado 2017.3 development environment. However, this concept could be transferred to virtually any version of Vivado, besides, the approach will work equally well for Ultrascale family as well.

We are offering this solution for a flat price of 24.99 USD which can be paid by Paypal.

What do you get after payment?

- Full source code of the working proof of concept example with echo TCP service including MDIO over GPIO driver;

- Set of TCL scripts for building PL and PS projects resulting in *.bin files with embedded first stage boot loader;

- Documentation in pdf format;

- Technical support over email/telegram channel;

NOTE: please allow some time for processing as we are working on logistic automation. In case of any concern please contact us.

Video tutorial

A walk-through of the project demonstrating how to drive MDIO lines by software driver in the form of a video tutorial is provided below:

Any questions? Ask in our Telegram channel:

https://t.me/magictale_electronics

Leave a Reply

You must be logged in to post a comment.